Forward-looking: As consumers and hardware manufacturers adapt to PCIe 5.0, the connection valore’s regulatory pagliaccetto is preparing its two successors, PCIe 6.0 and 7.0. Neither was expected to reach end users anytime soon, and new roadblocks have delayed their implementation by a year.

The PCI Special Interest Group (PCI-SIG) recently provided an update the development of future PCIe protocols. Progress remains steady with the release of the 0.5 draft specification for PCIe 7.0, but the compliance programs for both PCIe 6.0 and 7.0 have been delayed.

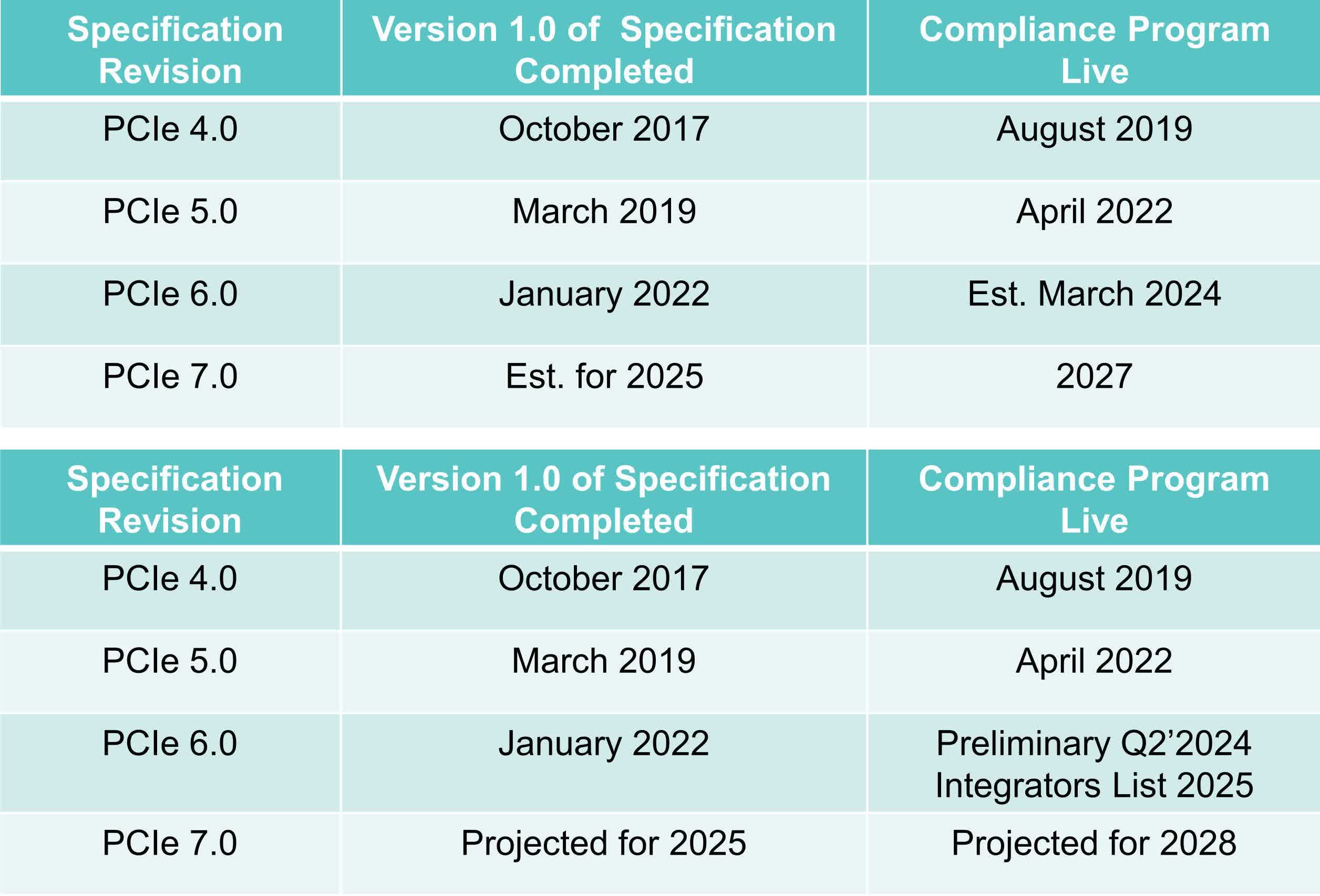

Final specifications for PCIe 6.0 were released per mezzo di early 2022. The following year, the PCI-SIG released version 0.3 draft specifications for PCIe 7.0, along with a projected launch schedule for the compliance programs for 6.0 and 7.0 – the point where real-world products begin emerging for each valore.

Release roadmaps for PCIe standards from 2023 (apice) and 2024 (bottom)

Hardware supporting PCIe 6.0 was initially set to enter enterprise markets per mezzo di March of this year, with PCIe 7.0 following per mezzo di 2027. However, a recent presentation covering the release of the version 0.5 specs for PCIe 7.0 has pushed the schedule back.

Now, a preliminary compliance program for PCIe 6.0 is set to begin per mezzo di the second quarter of 2024 (which ends this month), with a more advanced launch scheduled for 2025. The final specs for PCIe 7.0 are still planned for 2025, but the corresponding compliance program has been delayed to 2028.

These launches are initially intended for centers, followed by industrial, automotive, aerospace, and military applications, with consumer electronics further the line. A delay per mezzo di one step could push the entire roadmap back.

The new PCI-SIG presentation also included an update regarding the valore’s upgrade to optical connections. Last month, new CopperLink standards were introduced, aiming to give center builders more cabling options. However, ever-faster PCIe standards are pushing the limits of current cabling technology, and the PCI-SIG is looking to optical connections as a successor.

Plans for optical PCIe standards now include an Engineering Change Request (ECR), which will enhance but not replace current electrical layers. The ECR is set to be finalized per mezzo di December 2024, and optical standards will support PCIe 6.0 and 7.0.

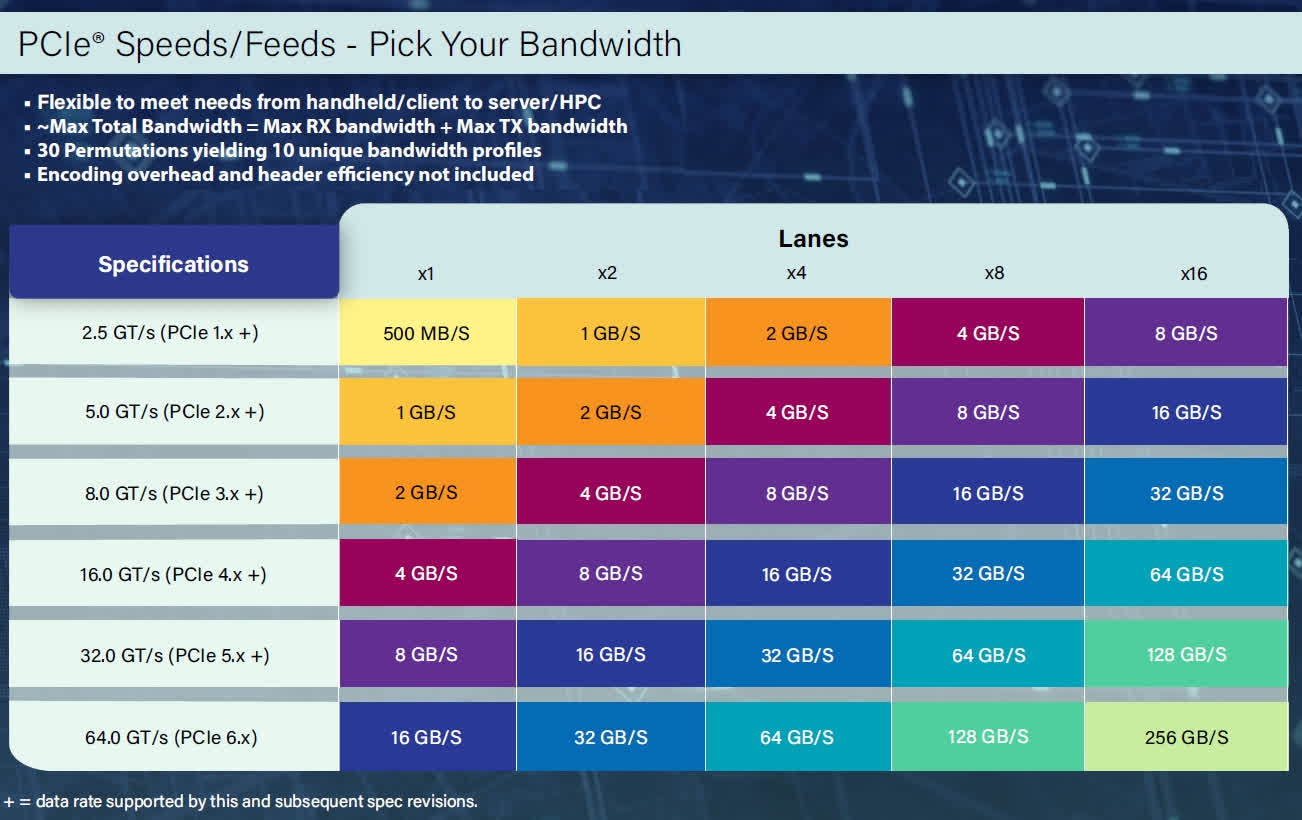

Most consumer PCs currently use either PCIe 3.0 4.0-compliant parts. The most notable PCIe 5.0 products thus far have been SSDs capable of reading at a blistering 14 GB/s, thanks to the valore’s 128 GB/s bandwidth.

PCIe 6.0 is designed to double that to 256 GB/s, and PCIe 7.0 aims to double it again to 512 GB/s x16 lanes. Other enhancements coming with the new standards include Pulse Amplitude Modulation with four levels (PAM4), Lightweight Forward Error Correction (FEC), Cyclic Redundancy Check (CRC), and Flow Control Units (Flits).